# SPIN-ON-GLASS BAKE AND CURE USING A RESISTIVELY HEATED BATCH ANNEALING OVEN

Woo Sik Yoo, Takashi Fukada, Yasuhide Hiraga, Kitaek Kang and Jiro Yamamoto\*

WaferMasters, Inc. 246 East Gish Road, San Jose, CA 95112 \* NEC Hiroshima Limited 5690 Yoshikawa, Happonmatsu, Higashi Hiroshima, Hiroshima, 739-0198 Japan

A five wafer batch annealing oven using a resistively heated, stacked hot plates was designed and tested for low temperature (100~450°C) annealing applications for 200mm wafers. The oven is designed to process five wafers simultaneously. Thermal properties of the 5 wafer batch annealing oven and wafer temperature profiles during low temperature annealing in stacked hot plates were characterized as a function of hot plate temperature. The stacked hot plate configuration makes convection between hot plates negligible and provides nearly isothermal environment for the wafer. Spin-on-glass (SOG) bake and cure processes were performed using a resistively heated batch annealing oven. Changes in film shrinkage and refractive index are characterized as a function of hot plate temperature index are characterized as a function of hot plate temperature.

#### **INTRODUCTION**

Spin-on-glass (SOG) is widely used and remains one of the most promising materials for low-cost inter-level planarization of VLSI multilevel interconnects. [1, 2] There are two basic types of SOG: siloxane-based organic SOG and silicate-based inorganic SOG. Both types of SOG involve spinning and annealing (baking and curing). Several low temperature (up to 400°C) thermal treatments are necessary to ensure that the desired thickness and physical property are obtained and the solvents are removed from the SOG.

Improper baking and curing very quickly could cause the upper layers of the SOG to be completely polymerized and prevent adequate moisture and/or solvent evaporation from the bulk of the SOG. In order to provide sufficient time for outgassing of the solvents and moisture, the baking and curing must be performed without causing any thermal shock. [1] Outgassing can cause trapping of hot and volatile compounds under a cap of fully polymerized SOG at the upper layer of the SOG. These trapped volatile compounds may then contribute to cracking and popping. [1, 3] A gradual increase in temperature is ideal for baking and curing cycle. The SOG is typically baked on hot plates and cured in batch furnaces. Thermal shock during the hot plate baking makes the process control difficult. A long process cycle and large batch size processing in batch furnaces poses cueing problem for small size production lots.

In this paper, a resistively heated batch annealing oven using stacked hot plates was proposed for low temperature  $(100 \sim 450^{\circ}C)$  annealing applications to improve productivity and lot size flexibility. Thermal properties of stacked hot plates including

wafer temperature profiles during low temperature annealing were characterized as a function of hot plate temperature. SOG films were annealed in batch annealing oven. Change in physical properties of SOG films before and after anneal was characterized as a function of temperature and time.

## **EXPERIMENTAL APARATUS**

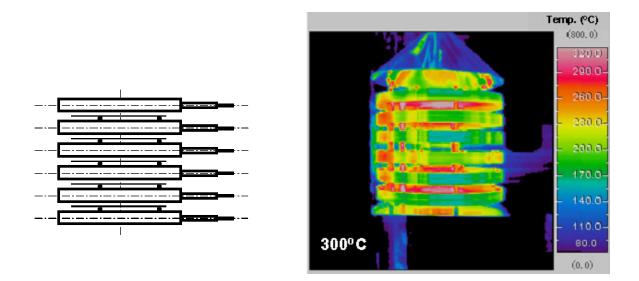

A resistively heated, stacked hot plate oven (batch annealing oven) was designed and tested for low temperature annealing applications in the temperature range of 100~450°C. The stacked hot plate oven was designed to provide single wafer signature, lot size flexibility and reasonable productivity at minimum facility requirement. Resistively heated hot plates were used to heat 200mm Si wafers in this study. The system is designed to process five wafers simultaneously. Figure 1 shows a side view of stacked hot plates with five Si wafers. This feature allows gradual heating of wafers required for low temperature annealing/baking applications without deteriorating productivity. The individual hot plate is made of aluminum and has an embedded heater for temperature control. The aluminum was chosen as the hot plate material because of its thermal stability in the temperature range up to  $450^{\circ}$ C, high thermal conductivity and ease of machining. The hot plate is slightly larger than the Si wafer in diameter and significantly thicker (30mm) than the Si wafer. Individual hot plates have three standoffs to keep the distance between a wafer and the hot plate. The standoffs are equally spaced on the perimeter of approximately 70% of wafer diameter. The gap between the hot plates is 20mm. During the process, wafers are placed on standoffs on the bottom hot plate. The wafers are located at in the middle of top and bottom hot plates (10mm above the bottom hot plate and 10mm below the bottom hot plate).

Fig. 1 Schematic diagram of stacked hot plates and thermal image of the hot plates at 300°C.

SOG annealing was done using the stacked hot plate annealing system. Organic SOG films on 200mm Si wafers with as spun thickness of 360nm were under 1 atm air. The SOG film shrinks up to 18~19% when it is fully out gassed. The annealing temperature was varied from 200°C to 400°C. The annealing time was also varied between 1 and 5 min. The film thickness shrinkage and refractive index change after annealing under different conditions were measured at 49 points on 200mm wafers using an ellipsometer.

#### **RESULTS AND DISCUSSION**

# Wafer Temperature Profile

The temperature uniformity of the hot plates was found to be very uniform. High thermal conductivity of aluminum prevents temperature gradient across the hot plates. The thermal conductivity of gases is 3 to 4 orders of magnitude lower than that of aluminum. [4, 5] The poor thermal conductivity of gases makes heat dissipation through the gas phase conduction smaller. The stacked hot plate configuration makes convection between hot plates negligible and provides nearly isothermal environment for the wafer.

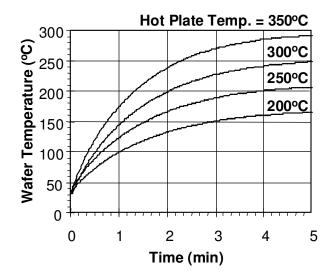

Wafer temperature profiles on hot plates were investigated as a function of hot plate configuration, standoff height, hot plate temperature and process atmosphere. [5] 200mm bare Si wafers with instrumentation thermocouples were annealed in the stacked hot plates at different temperatures under 1 atm air. The temperature of the six hot plates was controlled individually, but the temperature set points were kept the same. The wafer was placed on 8mm tall standoffs of the bottom hot plate. Temperature profiles of a wafer in stacked hot plates were measured at hot plate temperature set points of 200, 250, 300 and 350°C. Figure 2 shows the wafer temperature ramp up profiles in the stacked hot plates. Temperature uniformity within wafer and across 5 wafer load was found to be within  $+/-1^{\circ}C$ .

As the wafer is inserted in the stacked hot plates, the wafer temperature initially increases gradually and then it saturates at little below the hot plate temperatures. The heat transfer between the hot plates and the wafer is predominated by thermal conduction through the gas. Since the conduction heat transfer is one of the major heat transfer mechanisms at 1 atm air, the wafer temperature ramp up/down profile depends on ambient gas. When a high thermal conductivity gas such as H<sub>2</sub> and He is used as an ambient gas, the wafer temperature ramp rate and the saturated wafer temperature are higher than air, N<sub>2</sub>, O<sub>2</sub> and Ar. [5]

The direct contact between a wafer and a hot plate provides fast wafer temperature ramp up, but it results in ununiform wafer heating during temperature ramp up. When wafers with films deposited or coated at low temperatures are directly placed on a hot plate tend to slide during annealing due to the air bearing effect of out gassed species. By keeping an intentional gap between the hot plates and the wafer, good within wafer temperature uniformity can be obtained throughout the process. Wafer sliding can also be prevented. The wafer temperature profiles suggest that non-contact thermal annealing is gentle and provides repeatable process results. A nearly warpage free thermal annealing is achieved by placing a wafer on standoffs in stacked hot plates.

Fig. 2 Wafer temperature profiles during annealing process under 1 atm air.

## SOG Anneal

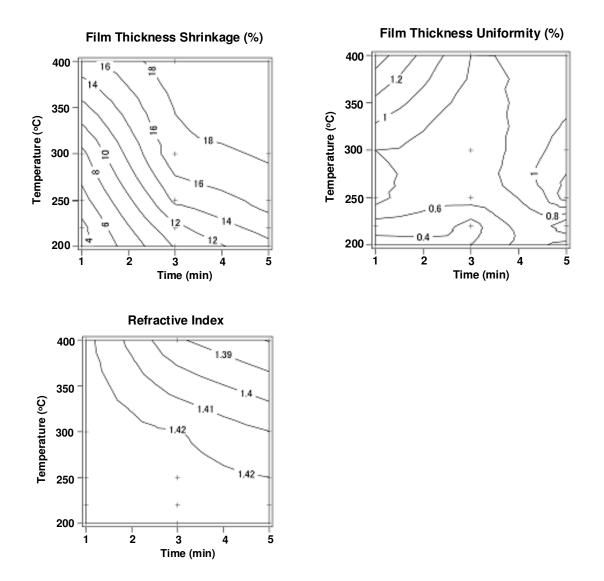

Complete out gassing without generating cracks in SOG films is desirable. To achieve this process goals, uniform and gradual heating of Si wafer for relatively long time (4~5min) is desirable. Incomplete baking or nonuniform baking result in poor uniformity in selectivity of etch rate in the following etch back process step. We were able to control SOG film properties using the batch annealing oven in the wide range of process conditions. Surface response plots of film shrinkage and uniformity after annealing under various process temperature and time are shown in Fig. 3. As annealing temperature and time increase, thickness shrinks more and refractive index decreases due to the film densification. Thickness shrinkage up to 19% was obtained. Average thickness uniformity of SOG films after annealing ranges from 0.5 to 1.5% in 1 $\sigma$ . Surface response patterns of film shrinkage and refractive index look quite similar. This suggests a strong correlation between film shrinkage and refractive index. Typical refractive index of as spun SOG films is ranging from 1.426 to 1.428. As annealing temperature and time increases, the film shrinks and the refractive index decreases. The refractive index of completely shrinked SOG films at 400°C for 5 min is around 1.390. Typical refractive index for thermally grown oxide is 1.460. [6]

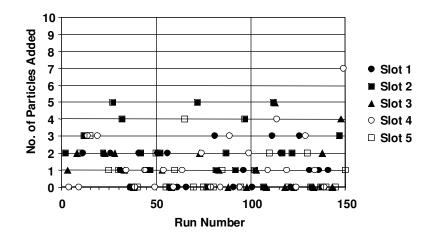

Particle performance of the system was measured regularly between production runs. Particle size over 0.2µm was measured. Figure 4 shows particle performance over extended period (over 4 months) in mass production environment. Excellent particle performance was obtained. Average number of particles added on a 200mm wafer is around 2. The particle performance of five individual slots was almost identical. Gentle heating of wafer and convection flow of outgassed species to the exhaust on top of the system helps in preventing particle generation in mass production environment. Sudden increase of particles in annealed SOG samples are well known problems in conventional single hot plate systems as well as large batch type furnaces. In case of single hot plate systems, very fast wafer temperature ramp up using direct contact between a wafer and a hot plate causes a large amount of outgassing and condensation of outgassed species on cold surfaces near wafer processing area. The fast outgassing and condensation causes sudden increase of particles in the conventional single hot plate systems. In case of large batch type furnaces, total amount of outgassing species from a large number of wafers in confined processing area makes the efficient exhaust of outgassing species difficult.

Fig. 3 Surface response plot of film shrinkage, uniformity and refractive index of SOG films after annealing under various process temperature and time.

Fig. 4 Particle performance in mass production environment.

The system used in this study is very compact (600mm (W) x 1200mm (D) x 1700mm (H)) and operates under 1 atm air and does not require any process gas, compressed air or cooling water. Average power consumption is less than 4kW at 400°C operation. Due to the 5 wafer simultaneous processing capability and gentle wafer temperature ramp up characteristics of the system, we are able to achieve very repeatable process results at higher productivity compared to conventional single hot plates and batch furnaces. Lot size flexibility is also improved compared to the batch furnaces without deteriorating productivity. Typical throughput for 3~5min process is 60~40wph. While throughput is maintained to a comparable level to conventional large batch furnaces, we were able to reduce wafer cycle time significantly and improved the lot size flexibility. The throughput and process results (i.e. uniformity and repeatability) are improved significantly compared to conventional single hot plates. The system provides lot size flexibility as well as productivity.

The low temperature batch annealing oven which employs six stacked hot plates showed very promising test results in various low temperature annealing processes such as Cu anneal, Al anneal, low k dielectrics anneal, and photoresist baking applications. It is also promising for low temperature annealing applications in GaAs and InP device fabrication processes. Chamber enclosure, process gases, vacuum pump and pressure control function can be added for processes which require precise process environment control.

### CONCLUSIONS

A five wafer batch annealing oven using resistively heated, stacked hot plates was designed and tested for low temperature (100~450°C) annealing applications for 200mm and 300mm wafers. Thermal properties of the annealing system and wafer temperature profiles during low temperature annealing in stacked hot plates were characterized as a function of hot plate temperature. The stacked hot plate configuration makes convection between hot plates negligible and provides nearly isothermal environment for the wafer. SOG films were annealed in the batch annealing oven. Changes in physical properties of

SOG films before and after anneal was characterized as a function of temperature and time. Productivity and lot size flexibility of batch annealing oven are compared with conventional hot plates and furnaces.

#### ACKNOWLEDGEMENTS

The authors would like to thank Mr. S. Fujimoto and T. Yamazaki of WaferMasters and Mr. T. Shimotani, Mr. Y. Shirotani, Mr. T. Kinoshita, Mr. K.Watanabe, Mr. H. Miyoshi and Mr. K. Aizawa of NEC Hiroshima Ltd. for their experimental arrangement and helpful discussions during this work.

#### REFERENCES

- 1. G.K. Rao, "Multilevel Interconnect Technology", (McGraw-Hill, New York, 1993) Chapter 2.

- 2. C.Y. Chang and S.M. Sze, "ULSI Technology", (McGraw-Hill, New York, 1996) Chapter 8.

- 3. R.F. Cook and E.G. Liniger, "Stress-Corrosion Cracking of Low-Dielectric-Constant Spin-On-Glass Thin Films", J. of Electrochem. Soc., 146, (1999) 4439.

- 4. "CRC Handbook of Chemistry and Physics" 75th Ed, ed. D.R. Lide, CRC Press (1994) Chap. 6 and Chap. 12.

- W.S. Yoo and T. Fukada, "Wafer Temperature Characterization during Low Temperature Annealing" 197th Electrochemical Society Proceedings Vol. 2000-9, (2000) 355.

- 6. S.Wolf and R.N. Tauber, "Silicon Processing for the VLSI Era" Vol. 1, (Lattice Press, Sunset Beach, California, 1986) Chapter 7.